Han-Carlson Adder Layout Generation using Open-Source RTL-to-Layout Flow

John Bryan

A 16-bit Han-Carlson adder layout is generated using a open-source RTL-to-Layout standard cell flow in Linux.

-

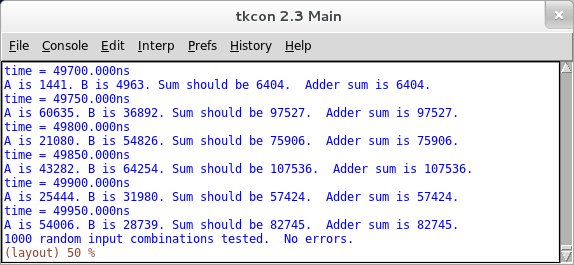

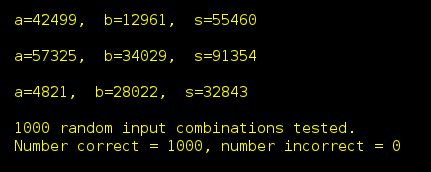

C code is written to produce the 16-bit Han-Carlson (HC) Verilog code. The Verilog code is compiled and simulated in Icarus.

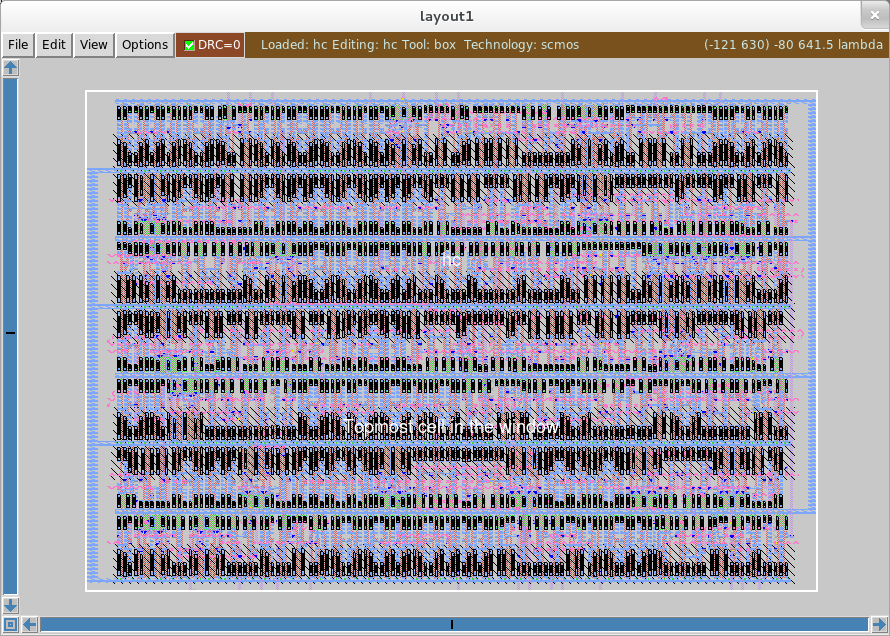

- The Qflow tutorial, from the Qflow site, is followed. Yosys synthesis, Vesta static timing analyzer, TimberWolf placement, Qrouter detailed routing. A HC DEF file is produced. The HC DEF file, OSU035 standard cell library LEF file, and the OSU035 standard cell library GDSII file are read into the Magic layout tool.

-

Passes DRC in Magic.

-

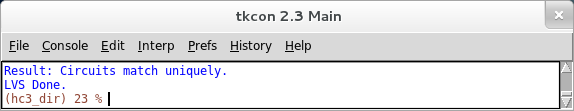

Passes LVS in Netgen. Compares post-Yosys synthesis spice netlist and post-Magic layout extraction spice netlist.

-

Extracted circuit passes Irsim simulation.